CMSIS Cortex-M3 Core Peripheral Access Layer Header File for NXP LPC17xx Device Series. More...

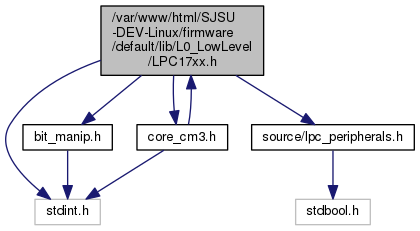

#include <stdint.h>#include "bit_manip.h"#include "source/lpc_peripherals.h"#include "core_cm3.h"

Go to the source code of this file.

Data Structures | |

| struct | LPC_SC_TypeDef |

| struct | LPC_PINCON_TypeDef |

| struct | LPC_GPIO_TypeDef |

| struct | LPC_GPIOINT_TypeDef |

| struct | LPC_TIM_TypeDef |

| struct | LPC_PWM_TypeDef |

| struct | LPC_UART_TypeDef |

| struct | LPC_UART0_TypeDef |

| struct | LPC_UART1_TypeDef |

| struct | LPC_SPI_TypeDef |

| struct | LPC_SSP_TypeDef |

| struct | LPC_I2C_TypeDef |

| struct | LPC_I2S_TypeDef |

| struct | LPC_RIT_TypeDef |

| struct | LPC_RTC_TypeDef |

| struct | LPC_WDT_TypeDef |

| struct | LPC_ADC_TypeDef |

| struct | LPC_DAC_TypeDef |

| struct | LPC_MCPWM_TypeDef |

| struct | LPC_QEI_TypeDef |

| struct | LPC_CANAF_RAM_TypeDef |

| struct | LPC_CANAF_TypeDef |

| struct | LPC_CANCR_TypeDef |

| struct | LPC_CAN_TypeDef |

| struct | LPC_GPDMA_TypeDef |

| struct | LPC_GPDMACH_TypeDef |

| struct | LPC_USB_TypeDef |

| struct | LPC_EMAC_TypeDef |

Typedefs | |

| typedef enum IRQn | IRQn_Type |

Enumerations | |

| enum | IRQn { NonMaskableInt_IRQn = -14, MemoryManagement_IRQn = -12, BusFault_IRQn = -11, UsageFault_IRQn = -10, SVCall_IRQn = -5, DebugMonitor_IRQn = -4, PendSV_IRQn = -2, SysTick_IRQn = -1, WDT_IRQn = 0, TIMER0_IRQn = 1, TIMER1_IRQn = 2, TIMER2_IRQn = 3, TIMER3_IRQn = 4, UART0_IRQn = 5, UART1_IRQn = 6, UART2_IRQn = 7, UART3_IRQn = 8, PWM1_IRQn = 9, I2C0_IRQn = 10, I2C1_IRQn = 11, I2C2_IRQn = 12, SPI_IRQn = 13, SSP0_IRQn = 14, SSP1_IRQn = 15, PLL0_IRQn = 16, RTC_IRQn = 17, EINT0_IRQn = 18, EINT1_IRQn = 19, EINT2_IRQn = 20, EINT3_IRQn = 21, ADC_IRQn = 22, BOD_IRQn = 23, USB_IRQn = 24, CAN_IRQn = 25, DMA_IRQn = 26, I2S_IRQn = 27, ENET_IRQn = 28, RIT_IRQn = 29, MCPWM_IRQn = 30, QEI_IRQn = 31, PLL1_IRQn = 32, USBActivity_IRQn = 33, CANActivity_IRQn = 34 } |

Detailed Description

CMSIS Cortex-M3 Core Peripheral Access Layer Header File for NXP LPC17xx Device Series.

- Version

- : V1.09

- Date

- : 17. March 2010

- Note

- Copyright (C) 2009 ARM Limited. All rights reserved.

- ARM Limited (ARM) is supplying this software for use with Cortex-M processor based microcontrollers. This file can be freely distributed within development tools that are supporting such ARM based processors.

- THIS SOFTWARE IS PROVIDED "AS IS". NO WARRANTIES, WHETHER EXPRESS, IMPLIED OR STATUTORY, INCLUDING, BUT NOT LIMITED TO, IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE APPLY TO THIS SOFTWARE. I SHALL NOT, IN ANY CIRCUMSTANCES, BE LIABLE FOR SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, FOR ANY REASON WHATSOEVER.

Macro Definition Documentation

| #define __I volatile const |

IO definitions

define access restrictions to peripheral registersdefines 'read only' permissions

| #define __IO volatile |

defines 'read / write' permissions

| #define __MPU_PRESENT 1 |

MPU present or not

| #define __NVIC_PRIO_BITS 5 |

Number of Bits used for Priority Levels

| #define __O volatile |

defines 'write only' permissions

| #define __Vendor_SysTickConfig 1 |

Set to 1 if different SysTick Config is used

| #define LPC_ADC ((LPC_ADC_TypeDef *) LPC_ADC_BASE ) |

| #define LPC_ADC_BASE (LPC_APB0_BASE + 0x34000) |

| #define LPC_AHB_BASE (0x50000000UL) |

| #define LPC_APB0_BASE (0x40000000UL) |

| #define LPC_APB1_BASE (0x40080000UL) |

| #define LPC_CAN1 ((LPC_CAN_TypeDef *) LPC_CAN1_BASE ) |

| #define LPC_CAN1_BASE (LPC_APB0_BASE + 0x44000) |

| #define LPC_CAN2 ((LPC_CAN_TypeDef *) LPC_CAN2_BASE ) |

| #define LPC_CAN2_BASE (LPC_APB0_BASE + 0x48000) |

| #define LPC_CANAF ((LPC_CANAF_TypeDef *) LPC_CANAF_BASE ) |

| #define LPC_CANAF_BASE (LPC_APB0_BASE + 0x3C000) |

| #define LPC_CANAF_RAM ((LPC_CANAF_RAM_TypeDef *) LPC_CANAF_RAM_BASE) |

| #define LPC_CANAF_RAM_BASE (LPC_APB0_BASE + 0x38000) |

| #define LPC_CANCR ((LPC_CANCR_TypeDef *) LPC_CANCR_BASE ) |

| #define LPC_CANCR_BASE (LPC_APB0_BASE + 0x40000) |

| #define LPC_CM3_BASE (0xE0000000UL) |

| #define LPC_DAC ((LPC_DAC_TypeDef *) LPC_DAC_BASE ) |

| #define LPC_DAC_BASE (LPC_APB1_BASE + 0x0C000) |

| #define LPC_EMAC ((LPC_EMAC_TypeDef *) LPC_EMAC_BASE ) |

| #define LPC_EMAC_BASE (LPC_AHB_BASE + 0x00000) |

| #define LPC_FLASH_BASE (0x00000000UL) |

| #define LPC_GPDMA ((LPC_GPDMA_TypeDef *) LPC_GPDMA_BASE ) |

| #define LPC_GPDMA_BASE (LPC_AHB_BASE + 0x04000) |

| #define LPC_GPDMACH0 ((LPC_GPDMACH_TypeDef *) LPC_GPDMACH0_BASE ) |

| #define LPC_GPDMACH0_BASE (LPC_AHB_BASE + 0x04100) |

| #define LPC_GPDMACH1 ((LPC_GPDMACH_TypeDef *) LPC_GPDMACH1_BASE ) |

| #define LPC_GPDMACH1_BASE (LPC_AHB_BASE + 0x04120) |

| #define LPC_GPDMACH2 ((LPC_GPDMACH_TypeDef *) LPC_GPDMACH2_BASE ) |

| #define LPC_GPDMACH2_BASE (LPC_AHB_BASE + 0x04140) |

| #define LPC_GPDMACH3 ((LPC_GPDMACH_TypeDef *) LPC_GPDMACH3_BASE ) |

| #define LPC_GPDMACH3_BASE (LPC_AHB_BASE + 0x04160) |

| #define LPC_GPDMACH4 ((LPC_GPDMACH_TypeDef *) LPC_GPDMACH4_BASE ) |

| #define LPC_GPDMACH4_BASE (LPC_AHB_BASE + 0x04180) |

| #define LPC_GPDMACH5 ((LPC_GPDMACH_TypeDef *) LPC_GPDMACH5_BASE ) |

| #define LPC_GPDMACH5_BASE (LPC_AHB_BASE + 0x041A0) |

| #define LPC_GPDMACH6 ((LPC_GPDMACH_TypeDef *) LPC_GPDMACH6_BASE ) |

| #define LPC_GPDMACH6_BASE (LPC_AHB_BASE + 0x041C0) |

| #define LPC_GPDMACH7 ((LPC_GPDMACH_TypeDef *) LPC_GPDMACH7_BASE ) |

| #define LPC_GPDMACH7_BASE (LPC_AHB_BASE + 0x041E0) |

| #define LPC_GPIO0 ((LPC_GPIO_TypeDef *) LPC_GPIO0_BASE ) |

| #define LPC_GPIO0_BASE (LPC_GPIO_BASE + 0x00000) |

| #define LPC_GPIO1 ((LPC_GPIO_TypeDef *) LPC_GPIO1_BASE ) |

| #define LPC_GPIO1_BASE (LPC_GPIO_BASE + 0x00020) |

| #define LPC_GPIO2 ((LPC_GPIO_TypeDef *) LPC_GPIO2_BASE ) |

| #define LPC_GPIO2_BASE (LPC_GPIO_BASE + 0x00040) |

| #define LPC_GPIO3 ((LPC_GPIO_TypeDef *) LPC_GPIO3_BASE ) |

| #define LPC_GPIO3_BASE (LPC_GPIO_BASE + 0x00060) |

| #define LPC_GPIO4 ((LPC_GPIO_TypeDef *) LPC_GPIO4_BASE ) |

| #define LPC_GPIO4_BASE (LPC_GPIO_BASE + 0x00080) |

| #define LPC_GPIO_BASE (0x2009C000UL) |

| #define LPC_GPIOINT ((LPC_GPIOINT_TypeDef *) LPC_GPIOINT_BASE ) |

| #define LPC_GPIOINT_BASE (LPC_APB0_BASE + 0x28080) |

| #define LPC_I2C0 ((LPC_I2C_TypeDef *) LPC_I2C0_BASE ) |

| #define LPC_I2C0_BASE (LPC_APB0_BASE + 0x1C000) |

| #define LPC_I2C1 ((LPC_I2C_TypeDef *) LPC_I2C1_BASE ) |

| #define LPC_I2C1_BASE (LPC_APB0_BASE + 0x5C000) |

| #define LPC_I2C2 ((LPC_I2C_TypeDef *) LPC_I2C2_BASE ) |

| #define LPC_I2C2_BASE (LPC_APB1_BASE + 0x20000) |

| #define LPC_I2S ((LPC_I2S_TypeDef *) LPC_I2S_BASE ) |

| #define LPC_I2S_BASE (LPC_APB1_BASE + 0x28000) |

| #define LPC_MCPWM ((LPC_MCPWM_TypeDef *) LPC_MCPWM_BASE ) |

| #define LPC_MCPWM_BASE (LPC_APB1_BASE + 0x38000) |

| #define LPC_PINCON ((LPC_PINCON_TypeDef *) LPC_PINCON_BASE ) |

| #define LPC_PINCON_BASE (LPC_APB0_BASE + 0x2C000) |

| #define LPC_PWM1 ((LPC_PWM_TypeDef *) LPC_PWM1_BASE ) |

| #define LPC_PWM1_BASE (LPC_APB0_BASE + 0x18000) |

| #define LPC_QEI ((LPC_QEI_TypeDef *) LPC_QEI_BASE ) |

| #define LPC_QEI_BASE (LPC_APB1_BASE + 0x3C000) |

| #define LPC_RAM_BASE (0x10000000UL) |

| #define LPC_RIT ((LPC_RIT_TypeDef *) LPC_RIT_BASE ) |

| #define LPC_RIT_BASE (LPC_APB1_BASE + 0x30000) |

| #define LPC_RTC ((LPC_RTC_TypeDef *) LPC_RTC_BASE ) |

| #define LPC_RTC_BASE (LPC_APB0_BASE + 0x24000) |

| #define LPC_SC ((LPC_SC_TypeDef *) LPC_SC_BASE ) |

| #define LPC_SC_BASE (LPC_APB1_BASE + 0x7C000) |

| #define LPC_SPI ((LPC_SPI_TypeDef *) LPC_SPI_BASE ) |

| #define LPC_SPI_BASE (LPC_APB0_BASE + 0x20000) |

| #define LPC_SSP0 ((LPC_SSP_TypeDef *) LPC_SSP0_BASE ) |

| #define LPC_SSP0_BASE (LPC_APB1_BASE + 0x08000) |

| #define LPC_SSP1 ((LPC_SSP_TypeDef *) LPC_SSP1_BASE ) |

| #define LPC_SSP1_BASE (LPC_APB0_BASE + 0x30000) |

| #define LPC_TIM0 ((LPC_TIM_TypeDef *) LPC_TIM0_BASE ) |

| #define LPC_TIM0_BASE (LPC_APB0_BASE + 0x04000) |

| #define LPC_TIM1 ((LPC_TIM_TypeDef *) LPC_TIM1_BASE ) |

| #define LPC_TIM1_BASE (LPC_APB0_BASE + 0x08000) |

| #define LPC_TIM2 ((LPC_TIM_TypeDef *) LPC_TIM2_BASE ) |

| #define LPC_TIM2_BASE (LPC_APB1_BASE + 0x10000) |

| #define LPC_TIM3 ((LPC_TIM_TypeDef *) LPC_TIM3_BASE ) |

| #define LPC_TIM3_BASE (LPC_APB1_BASE + 0x14000) |

| #define LPC_UART0 ((LPC_UART0_TypeDef *) LPC_UART0_BASE ) |

| #define LPC_UART0_BASE (LPC_APB0_BASE + 0x0C000) |

| #define LPC_UART1 ((LPC_UART1_TypeDef *) LPC_UART1_BASE ) |

| #define LPC_UART1_BASE (LPC_APB0_BASE + 0x10000) |

| #define LPC_UART2 ((LPC_UART_TypeDef *) LPC_UART2_BASE ) |

| #define LPC_UART2_BASE (LPC_APB1_BASE + 0x18000) |

| #define LPC_UART3 ((LPC_UART_TypeDef *) LPC_UART3_BASE ) |

| #define LPC_UART3_BASE (LPC_APB1_BASE + 0x1C000) |

| #define LPC_USB ((LPC_USB_TypeDef *) LPC_USB_BASE ) |

| #define LPC_USB_BASE (LPC_AHB_BASE + 0x0C000) |

| #define LPC_WDT ((LPC_WDT_TypeDef *) LPC_WDT_BASE ) |

| #define LPC_WDT_BASE (LPC_APB0_BASE + 0x00000) |

Typedef Documentation

Enumeration Type Documentation

| enum IRQn |

| Enumerator | |

|---|---|

| NonMaskableInt_IRQn |

2 Non Maskable Interrupt |

| MemoryManagement_IRQn |

4 Cortex-M3 Memory Management Interrupt |

| BusFault_IRQn |

5 Cortex-M3 Bus Fault Interrupt |

| UsageFault_IRQn |

6 Cortex-M3 Usage Fault Interrupt |

| SVCall_IRQn |

11 Cortex-M3 SV Call Interrupt |

| DebugMonitor_IRQn |

12 Cortex-M3 Debug Monitor Interrupt |

| PendSV_IRQn |

14 Cortex-M3 Pend SV Interrupt |

| SysTick_IRQn |

15 Cortex-M3 System Tick Interrupt |

| WDT_IRQn |

Watchdog Timer Interrupt |

| TIMER0_IRQn |

Timer0 Interrupt |

| TIMER1_IRQn |

Timer1 Interrupt |

| TIMER2_IRQn |

Timer2 Interrupt |

| TIMER3_IRQn |

Timer3 Interrupt |

| UART0_IRQn |

UART0 Interrupt |

| UART1_IRQn |

UART1 Interrupt |

| UART2_IRQn |

UART2 Interrupt |

| UART3_IRQn |

UART3 Interrupt |

| PWM1_IRQn |

PWM1 Interrupt |

| I2C0_IRQn |

I2C0 Interrupt |

| I2C1_IRQn |

I2C1 Interrupt |

| I2C2_IRQn |

I2C2 Interrupt |

| SPI_IRQn |

SPI Interrupt |

| SSP0_IRQn |

SSP0 Interrupt |

| SSP1_IRQn |

SSP1 Interrupt |

| PLL0_IRQn |

PLL0 Lock (Main PLL) Interrupt |

| RTC_IRQn |

Real Time Clock Interrupt |

| EINT0_IRQn |

External Interrupt 0 Interrupt |

| EINT1_IRQn |

External Interrupt 1 Interrupt |

| EINT2_IRQn |

External Interrupt 2 Interrupt |

| EINT3_IRQn |

External Interrupt 3 Interrupt |

| ADC_IRQn |

A/D Converter Interrupt |

| BOD_IRQn |

Brown-Out Detect Interrupt |

| USB_IRQn |

USB Interrupt |

| CAN_IRQn |

CAN Interrupt |

| DMA_IRQn |

General Purpose DMA Interrupt |

| I2S_IRQn |

I2S Interrupt |

| ENET_IRQn |

Ethernet Interrupt |

| RIT_IRQn |

Repetitive Interrupt Timer Interrupt |

| MCPWM_IRQn |

Motor Control PWM Interrupt |

| QEI_IRQn |

Quadrature Encoder Interface Interrupt |

| PLL1_IRQn |

PLL1 Lock (USB PLL) Interrupt |

| USBActivity_IRQn | |

| CANActivity_IRQn | |

1.8.11

1.8.11